ニュース&イベント NEWS & EVENTS

有機トランジスタの集積課題を克服

~複数の論理演算回路を単一素子で実現~

国立研究開発法人物質・材料研究機構

概要

1. 東京理科大学と物質・材料研究機構(以下NIMS)の研究グループは、アンチ・アンバイポーラトランジスタと呼ばれる特殊な有機トランジスタを用い、5つの2入力論理演算回路(AND, OR, NAND, NOR, XOR)を単一トランジスタで実証することに成功しました。2つの入力電圧を調整することで種々の論理演算回路を電気的に切り替えられるため、再構成可能な論理演算回路として利用できます。有機材料のもつ軽量性と回路設計の柔軟性を活かした高性能モバイル端末の開発に繋がると期待されます。

2. 情報量が飛躍的に増大するInternet of Things (IoT) 社会において軽量性と高い情報処理能力を兼ね備えた高性能モバイル端末の開発が求められています。有機トランジスタを集積した有機集積回路は、その基幹技術として期待されていますが、既存の微細加工技術が適応できないため、その集積度は極めて低いという課題がありました。

3. 上記課題に対し、本研究グループは、ある一定以上のゲート電圧を印加するとドレイン電流が減少する特殊な有機トランジスタ(アンチ・アンバイポーラトランジスタ)をデュアルゲート型トランジスタへ拡張し、2入力論理演算回路として応用しました。

4. トップゲートおよびボトムゲート電圧を入力電圧とし、ドレイン電流を出力信号とすることで5つの2入力論理回路動作を単一トランジスタで、しかも室温で実証することに成功しました。既存の集積回路では、NAND回路を形成するために4個、XOR回路を形成するためには12個のトランジスタを必要としますが、本提案素子では一つのトランジスタで実現できるため、大幅な素子数の削減に繋がります。これまで有機エレクトロニクスが苦手としてきた有機集積回路の高性能化が期待できます。

今後、入力電圧により種々の論理演算回路を電気的に切り替えられる特徴を活かして再構成可能集積回路へ応用することを目指します。

5. 本研究は、NIMS-東京理科大学連携大学院制度のもと、NIMS国際ナノアーキテクトニクス研究拠点 量子デバイス工学グループの早川竜馬 主任研究員、中払周 主幹研究員、若山裕グループリーダー、東京理科大学 本間航介、金井要教授により行われました。また、本研究は、科学研究費補助金 基盤A「集積度の飛躍的な向上を目指した有機負性抵抗トランジスタの開発(研究代表者 若山裕)」(19H00866)の支援を得て行われました。

6. 本研究成果は、2022年2月10日付でAdvanced Materials誌にAccepted Articlesとしてオンライン公開されています。

研究の背景

インターネットを通してあらゆるモノが繋がるInternet of Things (IoT)(1)社会において、膨大な情報量を高速に処理するモバイル端末の開発が求められています。印刷技術を利用して大面積に安価に形成できる有機集積回路は、その基幹技術として期待されていますが、フォトレジストや有機溶剤を使用する既存の微細加工技術が適応できないため、その集積度は依然として低いままです。そのため、素子の微細化だけに依存しない新しい回路設計指針が求められています。

上記課題に対して、本研究グループはアンチ・アンバイポーラトランジスタ(2)と呼ばれる特殊な有機トランジスタに着目し、論理演算素子へ応用することを検討してきました。アンチ・アンバイポーラトランジスタは、p型半導体とn型半導体をチャネル中央部で一部分だけ重ね合わせたpn接合を形成することで、ある一定以上のゲート電圧を印加するとドレイン電流が減少する特異的な電気特性を示します。この電流の増減現象は負性抵抗トランジスタで見られますが、トンネル伝導を利用するため、その動作温度は低温領域に限られてきました。一方、アンチ・アンバイポーラトランジスタでは室温において負性抵抗トランジスタ(3)と類似した電気特性を発現できるため、様々な論理回路へ応用することができます。

今回、本研究グループは、複数の論理回路動作を単体素子に担わせる多機能化により有機集積回路の高性能化に取り組みました。既存の集積回路では、p型トランジスタとn型トランジスタを一つの構成単位とし、それらを組み合わせることで論理回路を形成しています。例えば、2入力論理回路として代表的なNAND回路は4個のトランジスタで構成されています。また、XOR回路のような複雑な動作には12個のトランジスタを必要とします。これらの論理回路をより少ないトランジスタ数で実現できれば、素子の集積度を飛躍的に向上させることができます。

研究内容と成果

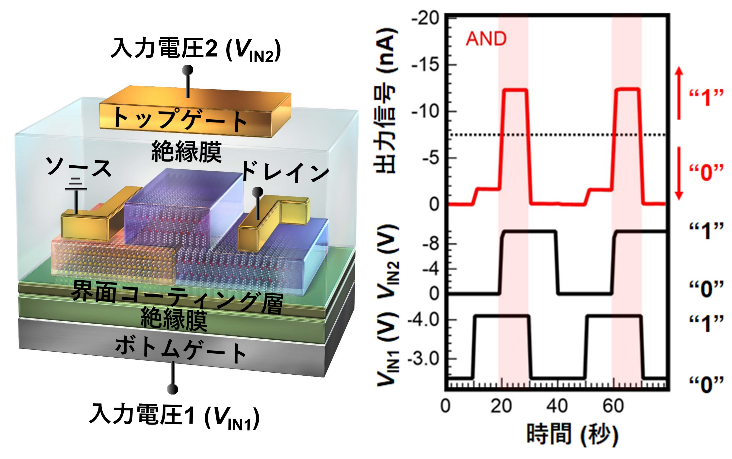

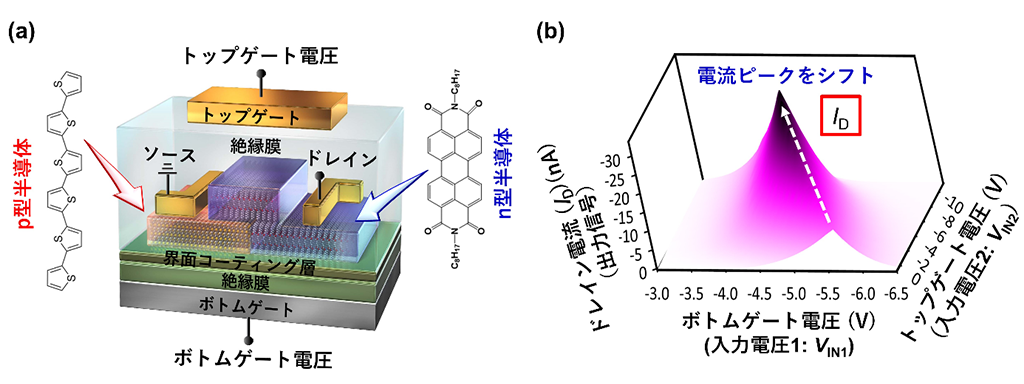

上記背景から、本研究グループは、これまで開発してきた有機アンチ・アンバイポーラトランジスタをデュアルゲート型トランジスタ(4)へ拡張し、2入力論理演算回路(5)へ応用しました。図1(a) に作製したトランジスタの素子構造を示します。ボトムゲート型トランジスタにトップゲート絶縁膜、さらにトップゲート電極を形成することで、デュアルゲート型トランジスタを作製しました。図1(b) に作製したトランジスタのドレイン電流-ゲート電圧特性を示します。ボトムゲート電圧を掃引することで、アンチ・アンバイポーラトランジスタに特徴的なΛ型のピークドレイン電流が観測されます。ここで重要な点は、ボトムゲート電圧により誘起されるドレイン電流のピーク電圧位置をトップゲート電圧により制御できることです。この特徴を活かして、ボトムゲート電圧を入力電圧1 (VIN1)、トップゲート電圧を入力電圧2 (VIN2)、ドレイン電流 (ID) を出力信号とすることで2入力論理演算回路を実現しました。

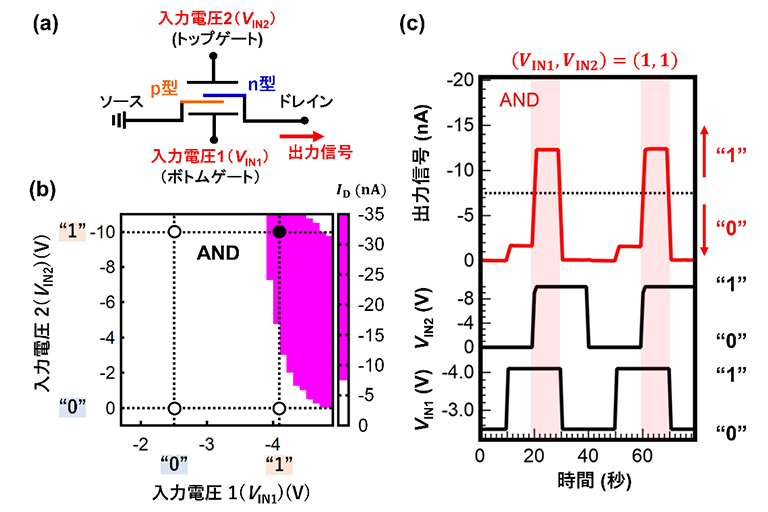

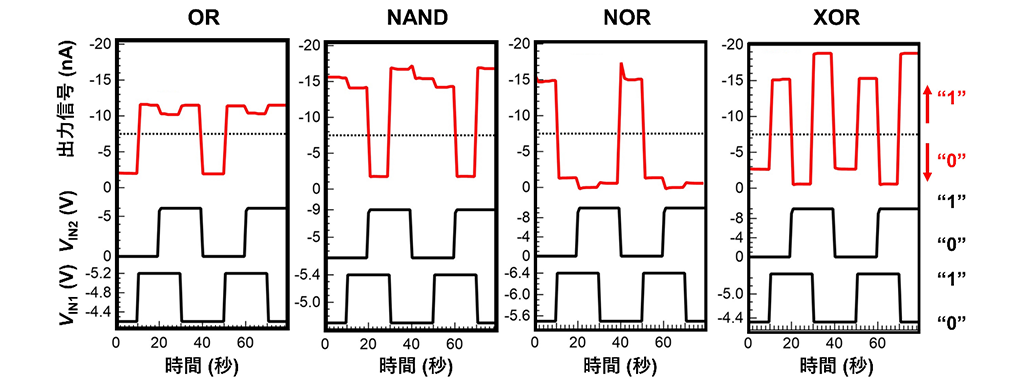

図2(a) にデュアルゲート型トランジスタと2入力論理演算素子との対応関係、図2(b) に入力電圧1 (VIN1)、入力電圧2 (VIN2)に対する出力信号 (ID) の2次元マッピングを示します。ここで0 < ID < −7.5 nAの場合を出力信号“0”、ID > −7.5 nA の場合を出力信号“1”とし、出力信号“1”に対応する領域を紫色で示しています。VIN1およびVIN2に対する“0”と“1”を図2(b) のように定義するとVIN1およびVIN2がどちらも“1”( (VIN1, VIN2) = (1, 1) ) のときにだけ出力信号が“1”となり、AND回路として動作することが示唆されます。実際に“0”と“1”に対応する入力電圧パルス (VIN1, VIN2) を印加すると、(VIN1, VIN2) = (1, 1) のときにだけ出力信号が“1”となり、AND回路として機能しました(図2(c))。さらに、入力電圧を最適化すると、OR, NAND, NOR, XOR回路を出力信号の定義を変えることなく実現できます (図3)。既存の集積回路では、NAND回路を形成するために4個、XOR回路には12個のトランジスタを必要としますが、本提案素子では一つのトランジスタで実現できるため、大幅な素子数の削減に繋がります。また、種々の論理回路を電気的に切り替えるため、再構成可能な論理回路へ応用できます。

このような論理回路動作は、単電子トランジスタ(6)に代表される量子効果トランジスタを用いてすでに提案されていますが、低温領域での素子動作に限られてきました。また、従来のトランジスタでは、ゲート電圧に対してドレイン電流が単調に増加するため、OR/AND、AND/NAND、NOR/NANDのように2つの論理回路しか切り替えられませんでした。本提案素子は、これらの課題を克服する新しい技術となります。

(c) 入力電圧1および2に対する AND回路動作。

今後の展開

今回、有機pn接合を利用した特殊なトランジスタ(アンチ・アンバイポーラトランジスタ)をデュアルゲート型トランジスタへ拡張し、2入力論理演算回路へ応用しました。トップゲートおよびボトムゲートを入力電極として用いることにより、5つの2入力論理演算回路(AND, OR, NAND, NOR, XOR)を単一トランジスタで実証することに成功しました。これまで有機デバイスが苦手としてきた集積回路の高性能化が期待できます。今後、入力電圧を調整することで種々の論理演算回路を電気的に切り替えられる特徴を活かして再構成可能コンピューティングへの応用が期待されます。現在の再構成可能集積回路(7)ではField Programmable Gate Array (FPGA)が主役となっていますが、従来の集積回路技術を利用しているため集積度には限界があります。本提案素子の動作原理を応用することで、さらに高性能なモバイル端末が実現できると期待されます。

論文情報

雑誌名

Advanced Materials

論文タイトル

Electrically Reconfigurable Organic Logic Gates: A Promising Perspective on a Dual-Gate Antiambipolar Transistor

著者

Ryoma Hayakawa, Kosuke Honma, Shu Nakaharai, Kaname Kanai, and Yutaka Wakayama*

掲載日時

令和4年 2月10日 (Accepted Articlesとしてオンライン掲載)

用語解説

(1) Internet of Things (IoT)

あらゆるモノにセンサを取り付け、インターネットを通してリアルタイムに収集した情報を社会活動に利用するネットワークシステムのことです。

(2) アンチ・アンバイポーラトランジスタ

p型半導体とn型半導体をチャネル中央部で一部分重ね合わせた構造を持つトランジスタで、ある一定以上のゲート電圧を印加するとドレイン電流が減少する特徴を持ちます。これは、p型トランジスタとn型トランジスタを直列接続した回路と等価となるため、両方のトランジスタがON状態のときにだけドレイン電流が流れることに由来します。負性抵抗と類似した電流の増減現象が室温で発現できるため、様々なデバイス応用が検討されています。

(3) 負性抵抗トランジスタ

ある一定以上のゲート電圧あるいはドレイン電圧を印加するとドレイン電流が減少する負性抵抗を利用するトランジスタです。p型半導体とn型半導体を接合したpn接合界面を流れるトンネル電流により負性抵抗が発現するため、低温領域での素子動作に限られています。

(4) デュアルゲート型トランジスタ

2つのゲート電極を有するトランジスタの総称です。本提案素子では、上部と下部にゲート電極を形成しています。

(5) 2入力論理演算回路

2つの入力信号に対して一つの信号を出力する論理演算回路でAND, OR, NAND, NOR, XOR, XNORの6種類があります。例えば、2つの入力信号がどちらも“1”のときにだけ出力信号が“1”となり、その他の入力信号の組み合わせでは、出力信号が“0”となる回路をAND回路といいます。このように入力信号に対する出力信号の組み合わせにより、OR, NAND, NOR, XOR, XNORに区別されています。既存の集積回路では、p型トランジスタとn型トランジスタを複数組み合わせて構成しています。例えば、NAND回路には4つ、XOR回路には12個のトランジスタを必要とします。

(6) 単電子トランジスタ

量子効果トランジスタの一種で、ソース-ドレイン間に量子ドットと呼ばれるナノメータースケールの粒子を配置した構造を持ちます。量子ドット内に一つの電荷が注入されるとクーロン反発により2個目の電荷が注入できなくなる現象を利用し、ドレイン電流を単一電荷レベルで制御できます。

(7) 再構成可能集積回路

集積回路を形成したあとでも回路構成を再構成できる論理回路の総称です。リコンフィギュラブル・コンピューティングとも呼ばれています。Field Programmable Gate Array (FPGA) がその代表例として知られています。

お問い合わせ

【研究内容に関すること】

国立研究開発法人物質・材料研究機構

国際ナノアーキテクトニクス研究拠点 ナノシステム分野 量子デバイス工学グループ

主任研究員 早川 竜馬 (はやかわ りょうま)

TEL: 029-860-4808 (直通), FAX: 029-860-4916

E-mail: HAYAKAWA.Ryoma【@】nims.go.jp

国立研究開発法人物質・材料研究機構

国際ナノアーキテクトニクス研究拠点

副拠点長 若山 裕 (わかやま ゆたか)

TEL: 029-860-4403 (直通), FAX: 029-860-4916

E-mail: WAKAYAMA.Yutaka【@】nims.go.jp

東京理科大学

理工学部 物理学科

教授 金井 要 (かない かなめ)

TEL: 04-7122-1481 (直通), FAX: 04-7123-9361

E-mail: kaname【@】rs.tus.ac.jp

【広報・報道に関すること】

国立研究開発法人物質・材料研究機構 経営企画部門 広報室

〒305-0047 茨城県つくば市千現1-2-1

TEL: 029-859-2026, FAX: 029-859-2017

E-mail: pressrelease【@】ml.nims.go.jp

東京理科大学 広報部 広報課

〒162-8601 東京都新宿区神楽坂1-3

TEL:03-5228-8107 FAX:03-3260-5823

E-mail: koho【@】admin.tus.ac.jp

【@】は@に置き換えてください。

研究室

金井研究室のページ:http://kanai-tus.jp/

金井教授のページ:https://www.tus.ac.jp/academics/teacher/p/index.php?6329

東京理科大学について

東京理科大学:https://www.tus.ac.jp/

詳しくはこちら