ニュース&イベント NEWS & EVENTS

量子Inspired技術の新展開:スケーラブルな全結合型イジング半導体システム

~組み合わせ最適化問題求解を低消費電力かつ高速に行う技術の基礎検証に成功~

研究の要旨とポイント

- 組み合わせ最適化問題を低消費電力かつ高速に解く技術として、量子Inspired技術のひとつである量子効果を用いないアニーリング方式が注目されています。

- 今回、アニーリング方式の全結合型イジング半導体システムの大規模化を実現するために、複数の集積回路(LSI)チップ用いたスケーラブル化技術の原理検証に成功しました。

- アニーリング方式では全結合スケーラブル化を実現した初めてのものとなります。

- 本研究を発展させカスタムLSIチップを用いて大容量化することで、新素材開発や創薬の分野で必要とされる高い性能を早期に実現できることが期待されます。

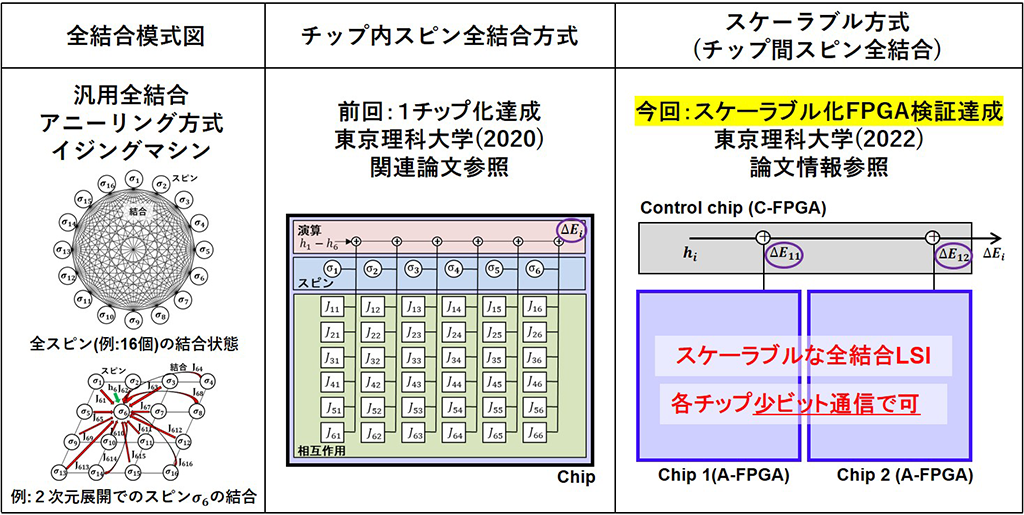

東京理科大学工学部電気工学科の河原尊之教授の研究グループは、量子Inspired技術の一つであるアニーリング方式の全結合型イジング半導体システムの大規模化を実現するために、複数の集積回路(LSI)チップ用いたスケーラブル化技術の原理検証に成功しました(図1)。

組み合わせ最適化問題(*1)は私たちの身近にも数多く存在していますが、従来コンピュータを用いて総当たり法で解くと膨大な計算資源が必要となります。この課題を解決できると期待されるのが、強磁性体の性質を表すイジングモデル(*2)に立脚した新しい計算手法です。これは、高温では磁化が発現していない強磁性体の乱雑な向きのスピンが温度を下げると、すべての可能性を試すことなく(すなわち総当たりではなく)相互の結び付きに従い、自然にスピンの向きが揃い磁化が発現するという性質を、組み合わせ最適化問題の解法に応用する試みです。これはアニーリング方式(*3)として知られています。

本研究では、少数のチップ間接続本数で複数の全結合イジングLSIチップを全結合のまま結合でき、全体でひとつの全結合システムとして動作する大規模イジングLSIシステムをスケーラブルに構成する方法を提案し、17個のFPGA(*4)チップで構成した384個の全結合スピンを備えた実機システムにて原理実証を行いました。この技術は、アニーリング方式としては初めて全結合スケーラブル化を実現した成果です。

将来的には、企業などと連携し、本技術を半導体設計技術の中核に発展させることを目指します。当研究室との共同研究に興味をお持ちの企業の方は、ぜひご連絡ください。

本研究成果は、2022年9月24日に国際学術誌「Microprocessors and Microsystems」にオンライン掲載されました。

研究の背景

アニーリング方式は、スピンとその結びつきを模したソフトウエア、もしくは本研究のようなこれらを模した半導体集積回路(LSI)や量子素子回路で実現しています。量子素子での開発が先行しましたので、LSIによる技術は量子Inspired技術のひとつとしても知られています。この量子Inspired技術は日本が得意な技術分野です。また、このとき強磁性体のモデルをそのまま利用するのではなく、すべてのスピンを結合させる全結合型とすることで、小実装面積(隣接結合では全結合スピン数の二乗個の数が必要)で実現でき、かつ、汎用性が高くなり(問題を解ける形に変換する手順が少ない)、広範囲の問題を解くことができます。

河原尊之教授の研究グループでは、この技術分野に2015年より学生の卒業研究テーマのひとつとして取り組み始めました。まず2016年国際学会IEEE NEWCAS 2016にて、修士課程に進学した学生が全結合型のLSI構成案を発表しました。その後、卒研・修士課程の研究として引き継がれ、2020年には新しいチップアーキテクチャにより512個の全結合型スピンを搭載した全結合型半導体アニーリング方式を搭載した人工知能集積回路(AIチップ)の発表(国際学会IEEE SAMI 2020)へと至りました(図1中、関連論文参照)。これは一次元スピン配列と二次元スピン間相互作用配列を用いて計算されたエネルギーに基づいてスピンの値を更新する全結合アニーリングプロセッサのLSI実装のためのアーキテクチャです。

しかしながら、ひとつのLSIに実装できるスピン数には限度があるため、問題の規模が制限されるという課題がありました。大規模な問題を解くためにはスピン数を増やす必要がありますが、単に複数のチップを用いてスピン数を増やそうとすると、事前に複数のチップに対応するようにスピン間の結合を全結合より変換して分解するか、または、全結合のままで多くのスピン同士の結合数分の配線でチップ間を接続しなければなりませんでした。この課題を解決するために、特別な方程式を導入する方式の発表は他機関でありましたが、アニーリング方式にてこれを打破する新しい発想が必要であり、続く卒研・修士課程の学生の研究テーマとなり、この度その成果が本研究として結実しました。

研究結果の詳細

今回、極めて少数のチップ間接続本数で、複数の全結合イジングLSIチップを結合し、アニーリング方式を用いたひとつの全結合システムとして動作する大規模イジングLSIシステムをスケーラブルに構成する方法を考案いたしました。さらにFPGAを用いてこの手法が正しく動作することを実証いたしました。アニーリング方式を用いた全結合型において、スケーラブル化を実現した初めてのものとなります。

今回開発した主要な技術は以下の通りです。

・エネルギー計算を分割して行いスピンを更新する手法を提案しました。2種類のチップを用い、同一の複数の第1のチップでエネルギーを分割して計算し、それらの合計をひとつの第2のチップで行って更新するスピンの値を決定する新しい方法です。全体でひとつの全結合システムとして動作します。第1と第2のチップ間のデータ通信の量を非常に少なくできることが特長です。原理は簡単ながら、これによりアニーリング方式として初めて、スケーラブルな全結合型システムが可能となりました。

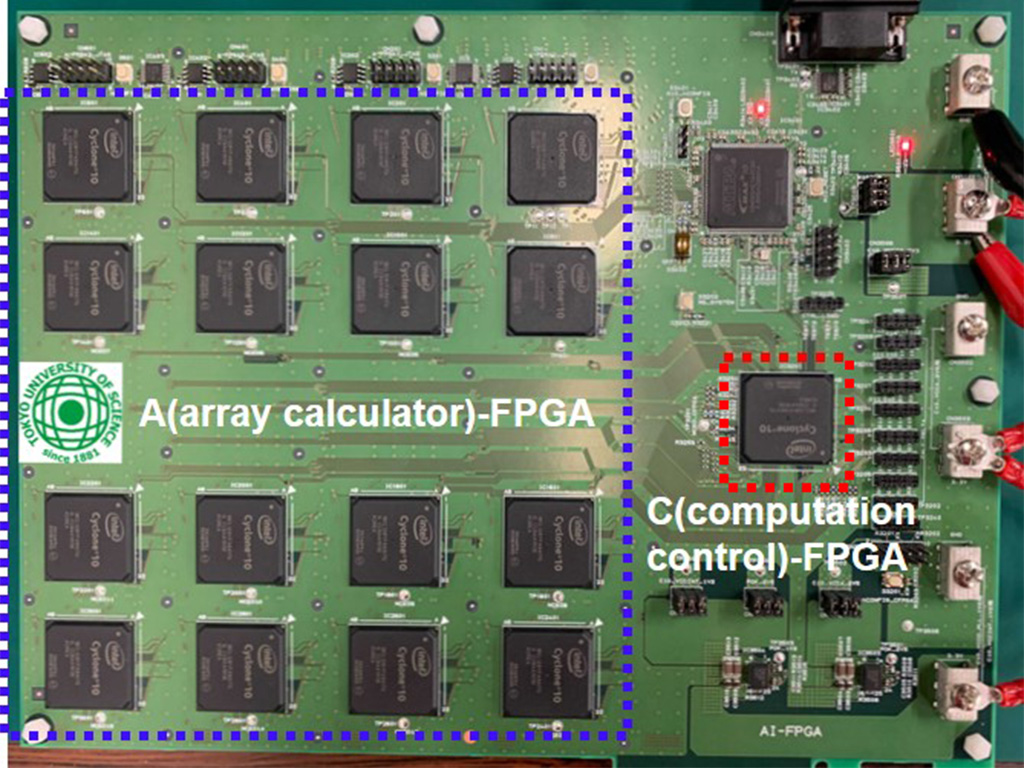

・実機での原理検証のために、第1のチップとして16個のFPGAチップ(A-FPGA)と、第2のチップとして1個のFPGAチップ(C-FPGA)とを用いて384スピンの完全結合アニーリング処理システムボードを作成しました(図2)。これにより、ひとつの全結合型LSIシステムとして動作しながら、少量の通信によって複数チップでの動作が可能であることを確認しました。

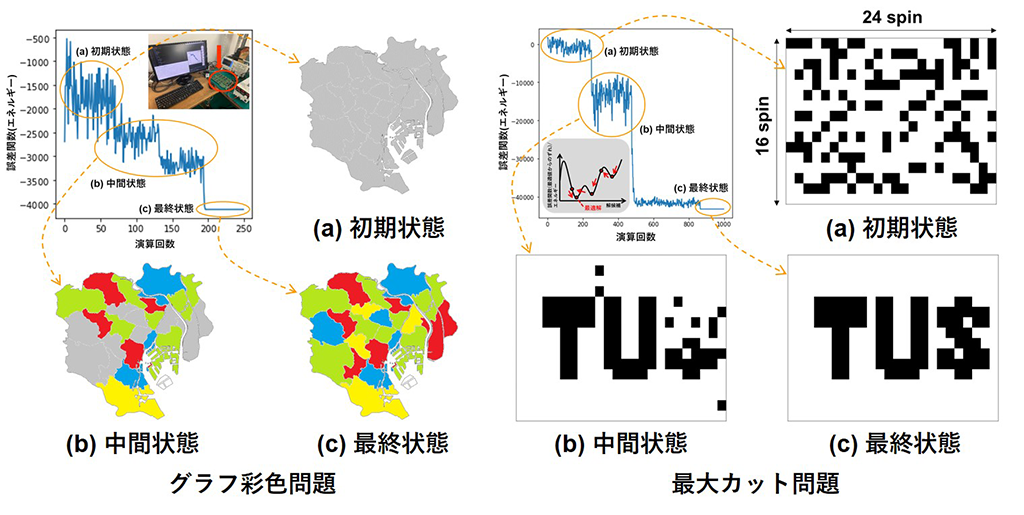

・92ノードのグラフ彩色問題と384ノードの最大カット問題が、この実機システムを使用して解けたことを示しました。最大カット問題においては、4GHz動作のCPUを持つPCで全結合アニーリング動作を模した計算よりも、584 倍高速で46 倍エネルギー効率が高い性能となりました(図3)。

今後の展望

今回、FPGAを用いた原理検証を成功させました。今後、カスタム設計のLSIチップを用いて大容量化して性能及び電力効率を大きく高めることで、新素材開発や創薬の分野で必要とされるような高い性能を早期に実現できます。今後は企業との共同研究につなげて本技術の社会実装を進め、日本の半導体復活へ向けた半導体設計技術の中核へと育てて行きます。

※本研究は、日本学術振興会科学研究費補助金(課題番号 22H01559)の助成を受けて実施したものです。

用語

*1 組み合わせ最適化問題

与えられた条件を満たす中で多数の選べる組合せの中から、ある価値において最も良いものをなるべく短時間で探し出す問題。

*2 イジングモデル

二つの状態をとるスピンが格子点に配置され、最隣接するスピン間の結合を考慮する模型。強磁性体のふるまいを説明できる。

*3 アニーリング方式

イジングモデルを応用して組み合わせ最適化問題を解く場合、解へ至るためにスピンの状態をあえて乱雑にするために温度という項目を導入し、次いでこの温度下げることで正しい解を得る。この過程が焼きなまし(アニーリング)に相当するためにアニーリング方式と呼ばれる。

*4 FPGA:Field Programmable Gate Array

予め用意された論理回路の組み合わせを製造後に変えることができ、所望の機能を実現できるLSI (半導体集積回路)。

論文情報

雑誌名

Microprocessors and Microsystems

論文タイトル

Scalable Fully Coupled Annealing Processing System and Multi-chip FPGA Implementation

著者

Kaoru Yamamoto, Takayuki Kawahara

DOI

※本論文はオープンアクセスです。どなたでもダウンロードできます。

関連論文

雑誌名

IEEE Transactions on Circuits and Systems I: Regular Papers

論文タイトル

Annealing Processing Architecture of 28-nm CMOS Chip for Ising Model With 512 Fully-coupled Spins

DOI

東京理科大学について

東京理科大学:https://www.tus.ac.jp/

詳しくはこちら