ニュース&イベント NEWS & EVENTS

超伝導量子コンピュータの新規回路方式

―量子チップ実装の大幅な簡素化を可能とする

~超伝導量子ビットを使用し、量子コンピュータの構築をめざす~

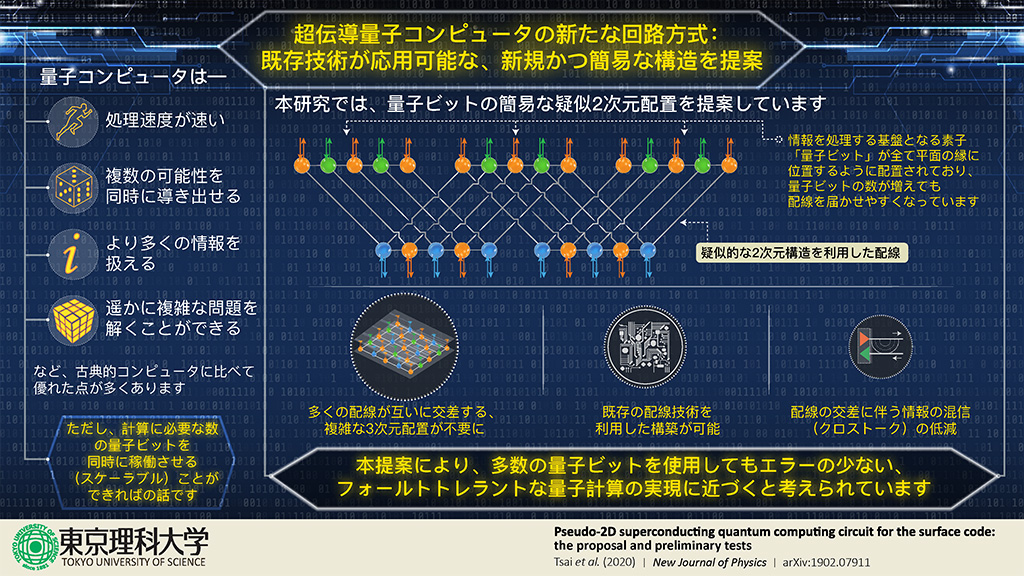

- ●量子コンピュータに使用される論理量子ビットの実装を容易にする新規回路方式を提示

- ●量子ビットの集積に向けた2次元平面配線による実装方式

- ●提案する回路方式は新規な3次元配線を必要とせず集積化の技術的工学的課題を低減

東京理科大学理学部第一部物理学科の蔡兆申教授らの研究グループは、現在のコンピュータより遥かに高速、省エネルギーな計算力に期待のかかる「量子コンピュータ」について、計算に使用する量子ビットの新たな回路方式を提示しました。

この量子コンピュータを構築するためには多数の量子ビットを組み合わせて「論理的な量子ビット」を実現する必要があります。これには2次元格子上に配置された量子ビットの集まりが必要で、この回路では隣り合う量子ビット同士がそれぞれ接続されています。論理的な能力を向上させるためにはより多くの量子ビットが必要ですが、量子ビットの数が増えればその分、必要な配線も増えます。特にチップの中心に位置する量子ビットには配線が届きにくくなります。この「配線問題」を解決するために、量子ビットに対して3次元(垂直)配線の研究が進められていますが、新規の技術であり、未だ技術的な課題があります。

今回提示された回路方式は、3次元(垂直)配線ではなく、従来の2次元格子状の配置を変形し、個々の配線を「平面」回路に実装可能にする方式です。この結果として、配線同士の交差が減り、交差に伴う情報の混信(クロストーク)も小さくすることができます。情報の損失やエラーを減らし、より信頼性のある量子ビットを集積することを可能にし、スケーラブルな量子コンピュータの実現に貢献すると考えられています。

|

研究の背景:量子コンピュータ・量子ビットとは

2019年9月、Googleが実証したと報じられた『量子スプレマシー(量子超越性)』(日本国内での一般報道は10月中旬)に代表されるように、計算速度を飛躍的に向上させる夢の技術として、近年量子コンピュータの名前を聞くことが増えてきました。

我々が一般的に使用しているコンピュータは、論理素子(ビット)の0と1の組み合わせによって情報を処理しています。多くの情報を処理するためには多くのビットが必要であり、コンピュータの演算処理装置(CPU)は初期の8ビットから16ビット、32ビット、現在では64ビットへと拡大されてきました。また、計算能力を更に拡大するために、世界各国が競って開発してきたのが、多数のCPUを搭載したコンピュータを並列に接続して運用するスーパーコンピュータです。2019年夏まで運用されていた日本の『京』もその1つでした。

しかし、どれほどビット数を増やしても、0と1だけのビットを使った「古典的な」コンピュータでは時間がかかってしまう種類の計算があります。大きな数の素因数分解や、巡回セールスマン問題がよく例として挙げられます。

量子コンピュータはこのような問題を解決し得る計算機として活発な研究が世界中で行われています。

研究の詳細

量子ビットの実現方法はいくつもありますが、そのうちの1つが今回の研究代表者である蔡教授らが1999年に開発した「超伝導量子ビット」です。冒頭にご紹介したGoogleの量子コンピュータにも、複数の超伝導量子ビットを集積した回路が使用されています。

この量子ビットが持つ量子の状態は、観測の影響だけでなく、量子ビットの周囲の環境などの影響によっても影響をうける為、量子ビットは古典的なビットと比べてエラーが起こりやすく、また多数の量子ビットを同時に稼働させることも容易ではありません。蔡教授らは現在、エラーが少なく、必要な計算に合わせて必要な数の量子ビットを稼働させられる(スケーラブルな)量子コンピュータの実現のため、多数の量子ビットを実装するための回路方式に着目した研究を行っています。

現存する多くの理論提案では、量子コンピュータは、量子ビットが2次元(平面)格子状に配置され、その他の配線や機器に接続されています。配置された量子ビットが増えると、2次元格子の中心付近に配置された量子ビットには操作や状態の測定のための配線を伸ばすことが難しくなってきます。そこで、主流な集積化の研究では3次元(垂直)配線による量子ビットへの個別配線が研究されています。しかしながら、3次元配線は未だ新しい技術であり、技術的な困難が残されていることも事実です。蔡教授は今回の研究について、「3次元の配線技術を必要とせず、完全に平面的な配置を維持できるような、超伝導量子ビットの集積回路方式を提示することで、この問題を解決したいと考えた」と動機を説明しています。

蔡教授らが提示したのは、量子ビットを「2次元に配置したまま」、全ての量子ビットへの配線も平面に配置する新しい回路方法です。これは、量子ビットの正方格子を、それぞれの並びごとに、巧妙に折り畳むことで「量子ビットが2列に並んだ(bi-linear array)」新たな配置ができあがります。この形状を取ることにより、2次元配置を崩さないまま、全ての量子ビットを縁に出して簡易な平面配線を実現できます。これによって配線間の混信や、損失が低減され、複数の量子ビットのエラーが抑えられ、それらで構成される論理量子ビットの信頼性の向上に繋がると期待されています。

2列に並んだ形であっても、元の隣り合う量子ビットのつながり方は維持する必要があり、そのために一部の量子ビットをつなぐ配線に交差が生じます。これは局所的な立体構造を使用することで実現できます。研究チームは、このような立体構造の寄与を調べ、評価しました。その結果、現状の技術を用いても十分に実現可能な回路であることが示されました。3次元配列を一切使わなくても、既存の2次元配列技術を応用して、量子コンピュータの実装が平面回路で実現可能であるということを示唆しています。

量子コンピュータは、計算力、消費電力などに関して、いずれ現在の「古典的」なコンピュータを上回る存在になるだろうと期待されており、量子ビットの改良や、データの処理のためのアルゴリズム、そして今回のような設計についてなど、世界中の多くの研究者が、それぞれのテーマで研究・開発競争を続ける非常にホットなテーマです。これからの展望について、蔡教授は「今回提示した配列の更なる可能性を追求するため、小規模な回路を構築して更に研究を続ける」意向を明らかにしています。

論文情報

| 雑誌名 | : | New Journal of Physics 2020年4月21日 オンライン掲載 |

|---|---|---|

| 論文タイトル | : | Pseudo-2D superconducting quantum computing circuit for the surface code: proposal and preliminary tests |

| 著者 | : | H. Mukai, K. Sakata, S. J. Devitt, R. Wang, Y. Zhou, Y. Nakajima, and J. S. Tsai |

| DOI | : | 10.1088/1367-2630/ab7d7d |

蔡 兆申 (TSAI JAW SHEN)教授

理学部第一部 物理学科

研究室のページ:https://www.rs.tus.ac.jp/tsai/

大学公式ページ:https://www.tus.ac.jp/fac_grad/p/index.php?6b06

東京理科大学について

東京理科大学:https://www.tus.ac.jp/

ABOUT:https://www.tus.ac.jp/info/index.html#houjin