| 研究テーマ |

-

進め方

当研究室では、卒研・修士学生の活動("教育")と権威ある国際学会採択レベルの"研究"との融合をめざしております。修士学生が筆頭でIEEE冠の国際学会で発表致します。ここへ至る経験が社会へ巣立つ彼らの成長の糧になると信じております。

学術面では、企業との共同研究にもつなげて成果の社会実装を進め、日本の半導体復活へ向けた半導体設計技術の中核へと育てて行ければと願います。

-

From 2025, LSI implementation of fully coupled Ising machines will be started as a compulsory student experiment

The Department of Electrical Engineering at Tokyo University of Science is thrilled to announce that, starting in 2025, it will introduce a cutting-edge fully-coupled Ising machine LSI (Large Scale Integration) system as a compulsory subject. This initiative is part of the university's ongoing commitment to enhance its curriculum and provide students with cutting-edge knowledge and skills in semiconductor design and optimization technologies.

Background on Ising Machines

They work by arranging "spins" to find the best way to minimize energy in the system. The fully-coupled Ising model is in high demand because of its incredible versatility in tackling all sorts of optimization challenges. Researchers at Tokyo University of Science have been actively promoting the research and development of LSI implementations of fully-coupled Ising machines for over a decade.

-

書籍:『人工知能チップ回路入門』(コロナ社)

☆2024年9月4日、『人工知能チップ回路入門』(コロナ社)が出版されました。

☆成長基幹産業である半導体や集積回路に興味を持ち、発展が期待されるエッジ側での人工知能(AI)による情報処理に関心のある若手技術者・高専・大学の学生の皆さんへおすすめな、手頃なページ数のAIチップ入門書です。3つの面からの入門レベルの内容です。

☆1.(2章~4章):ニューラルネットワークの基本的な説明から始め、電子回路の基本も概説した上で、回路ブロックレベルで人工知能チップの構成。各種ニューラルネットワークとして、2024年ノーベル賞対象技術であるホップフィールドネットワークやボルツマンマシンにも初歩的に簡単にだが触れている。

☆2.(5章、6章):高性能化に重要であるニアメモリコンピューティング、インメモリコンピューティング技術。

☆3.(7章、8章):全結合型イジングマシン技術(ニューラルネットワークのひとつであるホップフィールドネットワーク(2024年ノーベル賞対象技術)+アニーリング機構)。

☆下記URLより購入できます(既に9月4日より可)。

https://www.coronasha.co.jp/np/isbn/9784339009927/

リンクはしていないのでコピーされてお使いください。

-

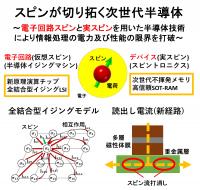

全結合型イジング半導体システム

社会の至る所で課題となる組合せ最適化問題を解く"全結合型"イジングマシンは、ニューラルネットワークのひとつであるホップフィールドネットワーク(2024年ノーベル賞対象技術の一つ)+アニーリング機構。この全結合型イジングマシンのLSI実装を検討。

2020年;一次元スピン配列と二次元スピン間相互作用配列を用いて計算されたエネルギーに基づいてスピンの値を更新する全結合アニーリングプロセッサのLSI実装のためのアーキテクチャ(NEDO先導調査研究2018-19)

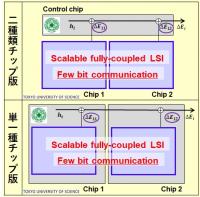

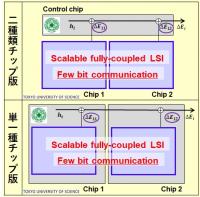

2022年(FPGA)、2024年(LSIシステム):チップ間接続本数で複数の全結合イジングLSIチップを全結合のまま結合でき、全体でひとつの全結合システムとして動作する大規模イジングLSIシステムをスケーラブルに構成するアーキテクチャ(下図。科研費22H01559、科研費23K22829)

-

Scalable Fully Coupled Annealing Processing System (Hopfield Network + Annealing mechanism)

A Hopfield network (one of the technologies eligible for the 2024 Nobel Prize) with an annealing mechanism is a fully coupled Ising system. Based on RikaDai's fully coupled Ising LSI system reported in 2020, we have developed a new scalable fully coupled Ising LSI system that combines all the basic spin cells and has excellent versatility and performance for solving the combinatorial optimization problem. Our development utilizes an epoch-making method that operates as a large-scale system by combining multiple fully coupled Ising LSI chips with an extremely small number of chip-to-chip connections and only a small amount of information transferred between chips. A system combining 16 FPGA chips is demonstrated.

本研究の一部は、日本学術振興会科学研究費補助金(課題番号 22H01559, 23K22829)の助成を受けて実施したものです。

-

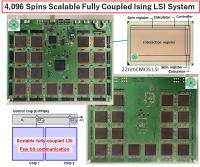

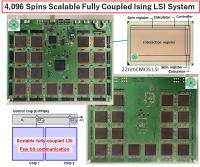

4,096 Spins Scalable Fully Coupled Ising LSI System (Hopfield Network + Annealing mechanism)

A fully coupled Ising system is a Hopfield network (one of the technologies eligible for the 2024 Nobel Prize). It includes an annealing mechanism. Toward the realization of a large-scale fully-coupled Ising semiconductor system, we have successfully verified a scalable technology using multiple LSI chips, setting a target for large capacity expansion.

This time, a scalable 4,096-spin fully-coupled Ising processing system was realized using 36 22nm CMOS computation LSI chips and a control FPGA.

Compared to an annealing emulation that mimics a fully connected Ising system on a PC, we achieved a 2,306-fold increase in performance, and a 2,186-fold increase in core units (CPU and computation chip).

本研究の一部は、日本学術振興会科学研究費補助金(課題番号 22H01559, 23K22829)の助成を受けて実施したものです。

-

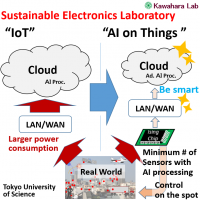

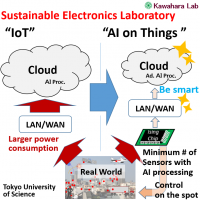

AI on Things ( ゜-゜)/゜AIonT

人工知能をモノに搭載しましょう。

日本が得意な"組み込みマイコン"の"AI化"でもあります。

または、どこでもAI、ユビキタスAI、・・・。

”AI on Things”: "Things" with advanced information-processing, artificial intelligence (AI), capability to lead to the evolution of current IoT society.

-

極低電力人工知能(AI)回路・システム

①比江嶋龍也、川島舜、柯夢南、河原尊之, "Swarm AIに基づく複数ロボットの同期行動と協調行動の有効性," 電子情報通信学会技術研究報告 (2020.1)、②Tatsuya Hiejima, Shun Kawashima, Mengnan Ke, Takayuki Kawahara, "Effectiveness of Synchronization and Cooperative Behavior of Multiple Robots Based on Swarm AI," IEEE APCCAS 2019 (2019.11)、③比江嶋龍也、河原尊之, "スウォーム人工知能に基づく掃除ロボット群の協調行動シミュレーション," 電子情報通信学会ソサイエティ大会 (2019.9)、④Akira Minamisawa, Ryoma Iimura, Takayuki Kawahara "High-speed Sparse Ising Model on FPGA," IEEE MWSCAS 2019 (2019.8)、 ⑤Yasuhiko Yoshida, Ryo Oiwa, Takayuki Kawahara "Ternary Sparse XNOR-net for FPGA Implementation," IEEE ISNE 2018 (2018.5)、⑥Yasushi Fukuda, Takayuki Kawahar "Stochastic Weights Binary Neural Networks on FPGA," IEEE ISNE 2018 (2018.5)、⑦吉田康彦、河原尊之, "IoT向け三値化ニューラルネットワークの検討," 電子情報通信学会研究会 (2017.12)、⑧Yasushi Fukuda, Zule Xu, Takayuki Kawahara "Robustness Evaluation of Restricted Boltzmann Machine against Memory and Logic Error," IEICE Transactions on Electronics (2017.12)、⑨Kenta Someya, Ryoto Ono, Takayuki Kawahara, "Novel Ising Model Using Dimension-Control for High-Speed Solver for Ising Machines," IEEE NEWCAS 2016 (2016.6)

-

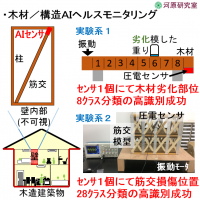

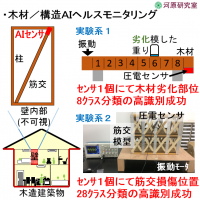

環境/建築(インフラ)/生体情報計測・情報処理システム

①Best Paper Award 受賞: Kohei Koike, Kenta Suzuki, Mengnan Ke, Kenjiro Mori, Takumi Ito, Takayuki Kawahara, "Damage-Position Identification of Wooden-House Models for Structural Health Monitoring Using Machine Learning," IEEE APCCAS 2020(2020.12)、②Kenta Suzuki, Kohei Koike, Mengnan Ke, Kenjiro Mori, Takumi Ito, Takayuki Kawahara, "Improvement of Generalization Performance for Timber Health Monitoring using Machine Learning," IEEE APCCAS 2020(2020.12)、③Ryota Tanida, Atsushi Yamamoto, Noriaki Takahashi, Natsuhiko Sakiyama, Sakuya Kishi, Takayuki Kishimoto, So Hasegawa, Kenjiro Mori, Yoichiro Hashizume, Jing Ma, Takashi Nakajima, Mikio Hasegawa, Takahiro Yamamoto, Takumi Ito, Takayuki Kawahara, "Machine Learning Classification Methods Using Data of 3-Axis Acceleration Sensors Equipped with Wireless Communication Means for Locating Wooden House Structural Damage," IEEE APCCAS 2019 (2019.11)、④Noriaki Takahashi, Natsuhiko Sakiyama, Takuji Yamamoto, Sakuya Kishi, Yoichiro Hashizume, Takashi Nakajima, Takahiro Yamamoto, Mikio Hasegawa, Takumi Ito, Takayuki Kawahara, "An Evaluation of Wooden House Health Monitoring System using PVDF Piezoelectric Sensor with 3-layer Neural Network and Inverted Binary-Data Augmentation," IEEE SAMI 2019 (2019.1)

-

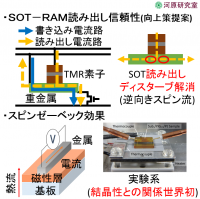

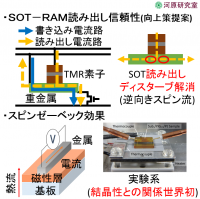

スピン流応用(SOT-RAM:科研費19K04536)

①Yuwa Kishi, Akihiro Yamada, Mengnan Ke, Takayuki Kawahara, "

Evaluation of Read Disturbance Reduction Effect by SOT-MRAM Bi-directional Read on Device Size Dependence" IEEE Intermag 2021 (2021.4)、②Yuwa Kishi, Keisuke Tabata, Mengnan Ke, Takayuki Kawahara, "Evaluation of Read Disturbance Reduction Effect by Bi-directional Read on Ferromagnetic Material Properties of SOT-MRAM," IEEE MMM 2020 (2020.11)、③Y. Kishi, M. Ke, M. Itoh, R. Kashiwa, T. Matsuzaki, T. Kawahara , "Impact of the metal/YIG interfaces in Pt/(W)/Y3Fe5O12/Gd3Ga5O12 and W/Y3Fe5O12/Gd3Ga5O12 structures for spin Seebeck effect," IEEE Intermag 2020 (2020.5)、④Atsushi Yamamoto, Takayuki Kawahara, "Evaluation of Spin Seebeck Effect in Single-crystal and Polycrystal Y3Fe5O12 (YIG)," IEEE MMM-Intermag (2019.1)、⑤Atsushi Yamamoto, Makoto Arai, Tetsuya Takimoto, Masatoshi Itoh, Takayuki Kawahara, "Evaluation of Correlation between Orientation of Y3Fe5O12 (YIG) Thin Film and Spin Seebeck Effect," 応用物理学会春季学術講演(2018.3)、⑥Atsushi Yamamoto, Makoto Arai, Tetsuya Takimoto, Masatoshi Itoh, Shizutoshi Ando, Shigeru Saito, Takayuki Kawahara, "Evaluation of Correlation Between Orientation of Y3Fe5O12(YIG) Thin Film and Spin Seebeck Effect," IEEE Intermag (2017.4)、⑧Hirokazu Kazama, Takayuki Kawahara, "Spin-Orbit Torque MRAM Read Reliability," IEEE Intermag

|